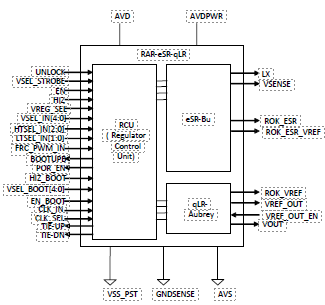

RAR-eSR-qLR-ref-1.62-3.63-0.55-2.5.04g_TSMC_40_uLP is a Retention Alternating Regulator in TSMC 40uLP embedding and controling two ViC regulators called eSR and qLR. The eSR is designed to provide dynamic power from 100 mA to 500 mA, depending on the eSR flavor. The qLR is used for data retention and very low power always-on circuitry (up to 1.0 mA). Both regulators are linked and the RAR embeds a Regulator Control Unit (RCU) that ensures that only one regulator is active at a given moment, while the other regulator output is set to high-impedance state.

Key Benefits

- Ideal regulator for power and voltage islets

- Embedded RCU (Regulator Control Unit) to manage booting and mode transitions and to ensure data integrity

- Configurable output drive before delivery to fit the application

- High Efficiency (up to 95% peak efficiency)

Key Features

| PARAMETERS | CONDITION |

Minimum value

|

Typical value

|

Maximum value

|

|---|---|---|---|---|

|

Input Voltage

|

- | 1.62 V | 3.63 V | |

|

Output Voltage

|

- | 0.55 V | 2.5 V | |

|

Output current configuration

|

- | - | 100 mA;200 mA;500 mA | - |

|

Quiescent current typical value

|

- | 100 µA | - | |

|

Accuracy

|

- | - | +/- 3% | |

|

PSRR

|

NA | - | NA | - |

Applications

- Smart Headset

- TWS Earpods

- Smart Speaker

- Home Appliance

- AR - VR

- Voice Assistant

- Infotainment

- Hearing aids

- Voice-controlled devices

- Bluetooth

- NB-IoT

- ULP MCU

- WiFi

- GNSS

- Cellular IoT

Key Performances

- Possibility to control the booting sequence even when the digital inputs are not yet valid. This function is particularly useful when the RAR supplies the ACU of the SoC. A proper starting sequence is guaranteed even if the ACU is not yet supplied.

- Can be used in different modes:

- - The Normal Mode: In this mode the eSR is activated and regulates the output. At the same time the qLR is inactivated and its output, VOUT, is set in high-impedance. In this mode the RAR can source up to 100 mA, 200 mA or 500 mA (depending on the embedded eSR).

- - The Retention Mode: In this mode the qLR is activated and regulates the output. At the same time the eSR is disactivated and its output, LX, is set in high-impedance.

- - The HIZ mode: The outputs of both regulators are in high-impedance state. In this case, the eSR is shut down to reduce the power consumption. HIZ Mode is set by asserting EN and HIZ.

- - The Pull-Down Mode, when both regulators are shut down to minimize the power consumption. Both regulator outputs are also pulled down to ground. This mode is set by de-asserting EN.

- - A internal integrated Local Supply Monitoring (LSM) function is also provided to ensure clean reinitialization if AVD drops below a certain threshold and then restored in a short period of time.

- High impedance (HIZ) mode keeps regulator output in a high impedance state to allow the output to be forced via either another regulator, a power switch, or any other mean, provided that the output voltage is kept between 0 V and VAV D.

- This product comes with all power pads required for AVD, AVDPWR, LX, VSENSE, GNDSENSE,

- and AVS ports, and includes their own ESD (Electro-Static Discharge) protection structures.

Technical information

- Technology: TSMC 40 uLP

- Embedded features:

- External clock